Vhdl Parallel To Serial Converter

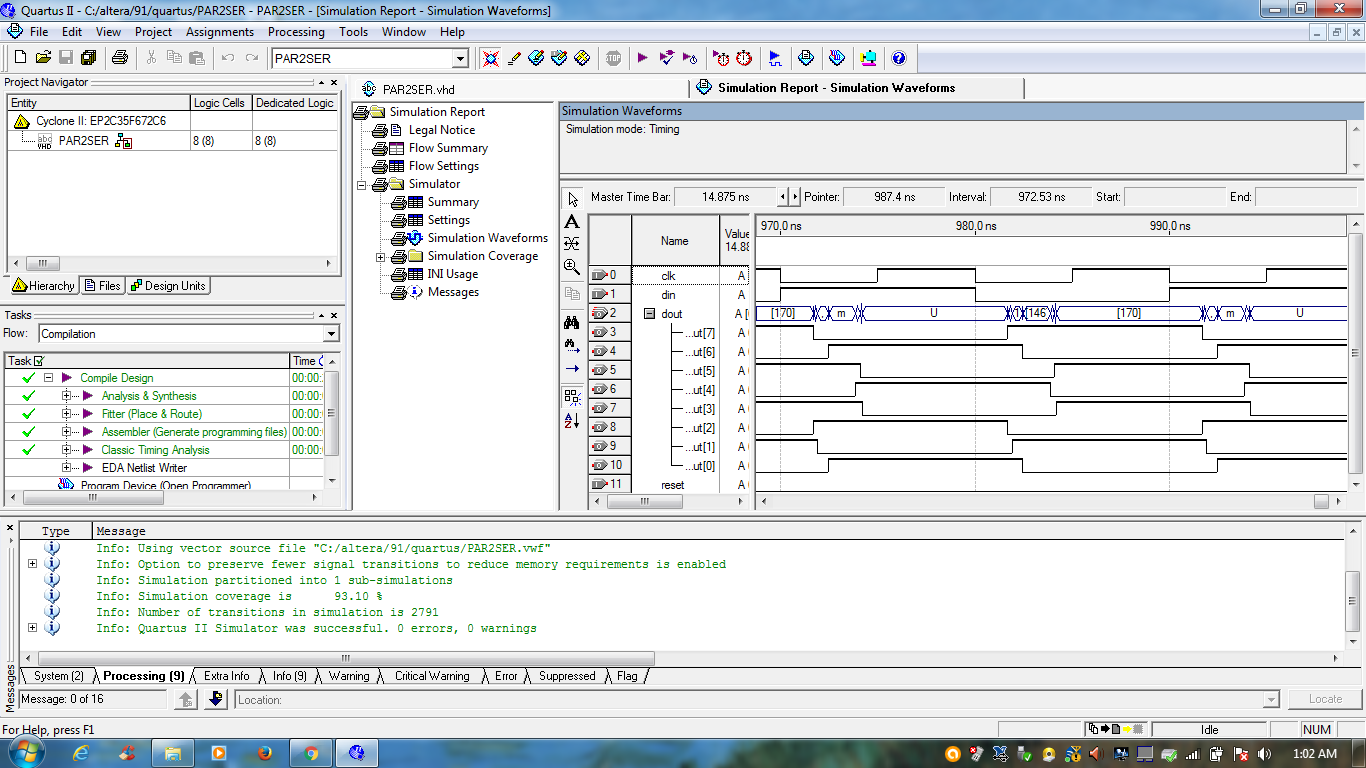

Practical VHDL samples. Par2ser.vhd par2ser Parallel to Serial Converter 4 Implements a simple parallel-serial converter- with load and shift left modes.

I am making a parallel to serial converter using ring counter in verilog. The ring counter is working fine but the Parallel to serial converter is not working properly and I am getting x undefined result. I am providing the code kindly help me finding the problem. TOP module PtoSTOP; reg clk,rst; wire 3:0 myout; wire out; Ring a(clk,rst,myout); parToser x(myout,clk,rst,out); initial begin clk=1; rst=1; #1 rst=0; end always #2 clk=clk; endmodule Parallel TO Serial Converter module parToser(myout,clk,rst,out); input clk,rst; input 3:0 myout; output reg out; reg 2:0i; always @(posedge clk or posedge rst) begin if(rst) begin out. I think the main issue you are seeing is part of parToser. You have reg 2:0i; which you increment and use to address input 3:0 myout; but i can hold values 0 to 7, half of which is outside the address range of 3:0 myout.

Serial To Parallel Converter

Serial To Parallel Adapter

You should be seeing a simulation error about out of range addressing. Also you have included a few flip-flops with a reset condition but not added the reset to the sensitivity list in 'parToser' & 'Ring': always @(posedge clk) Should be: always @(posedge clk or posedge rst) With out this trigger your out, i and myout variables will be x, as they have not been set to a known condition. NB: parToser i = i+1; should be i.